Verilog Code For And Gate In Behavioural Model 45+ Pages Summary [3.4mb] - Updated

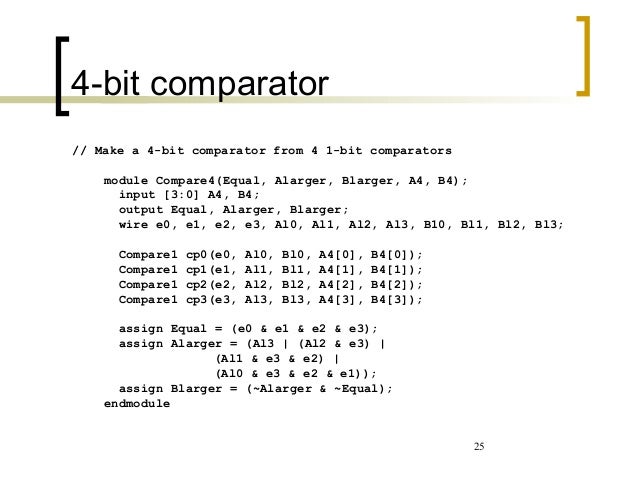

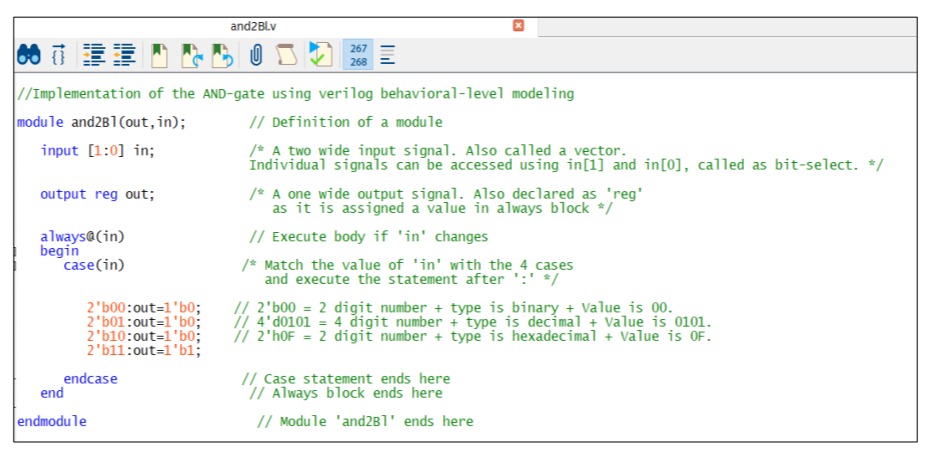

23+ pages verilog code for and gate in behavioural model 2.3mb. See Example 7 4 on page 11 4 The Behavioral or procedural level described below. 4-Bit Array Multiplier using structural Modeling. Wire x and wire y is the input to third OR gate as shown in the diagram below. Check also: code and learn more manual guide in verilog code for and gate in behavioural model Module 3_8_DEC input 30din output 70dout.

In this blog post we implement. Structural Modeling of D flip flop.

Full Adder Verilog Code In Structural Modelling

| Title: Full Adder Verilog Code In Structural Modelling |

| Format: eBook |

| Number of Pages: 204 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: August 2021 |

| File Size: 3.4mb |

| Read Full Adder Verilog Code In Structural Modelling |

|

Verilog Code for 38 Decoder using Case statement Decoders are combinational circuits used for breaking down any combination of inputs to a set of output bits that are all set to 0 apart from one output bit.

Module decoder_3to8 input 20 a output 7. In the above Verilog code we have used wire concept. Then we use assign statement to write the logical expression for NAND. Wires are used to connect modules just like on the breadboard. Verilog Code Logic Gate Dataflow modeling and gate or gate not gate nor gate xor gate xnor gate nand gate. The input and output ports are then declared.

Demux 1 To 4 Gate Level Verilog Code

| Title: Demux 1 To 4 Gate Level Verilog Code |

| Format: PDF |

| Number of Pages: 306 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: December 2017 |

| File Size: 3.4mb |

| Read Demux 1 To 4 Gate Level Verilog Code |

|

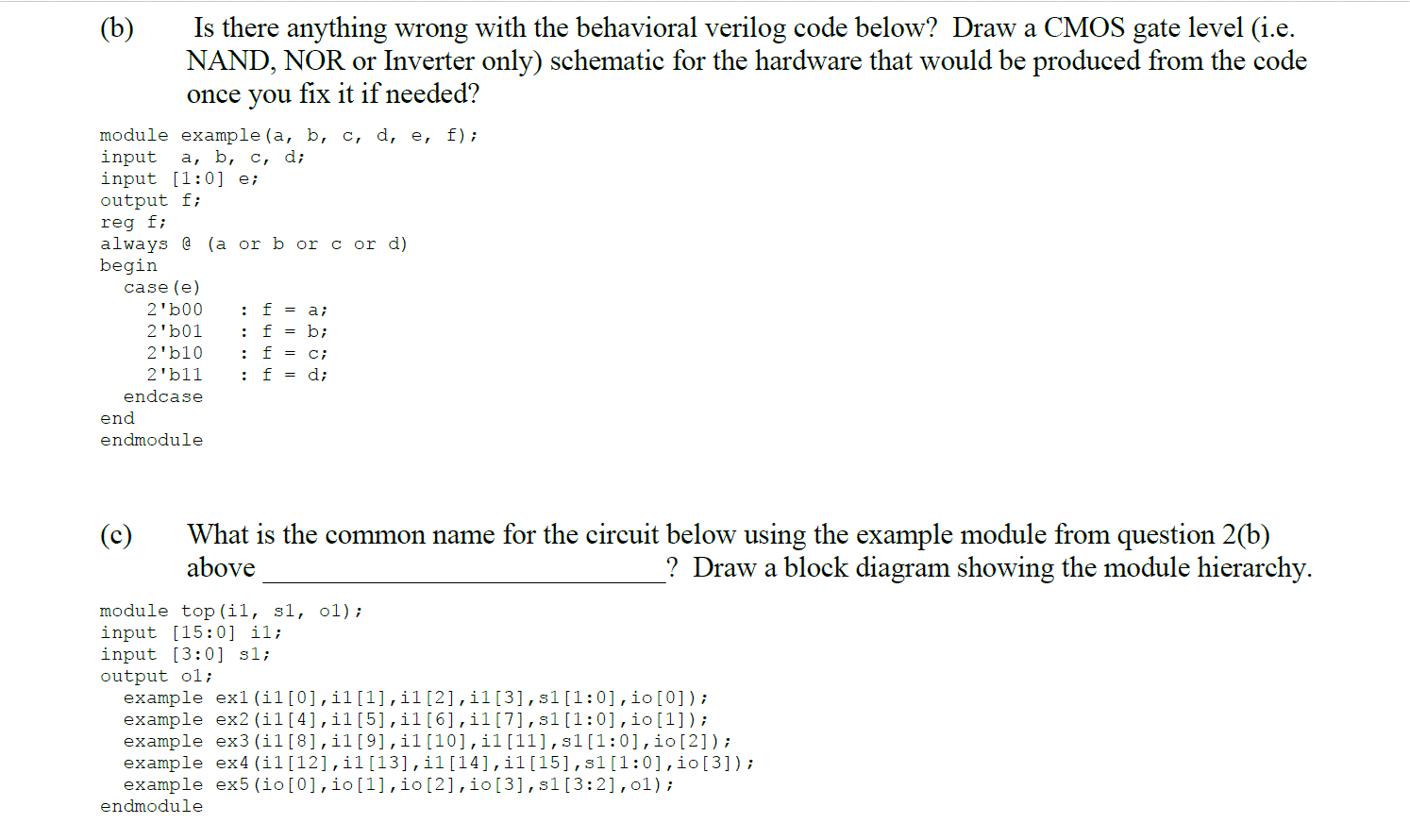

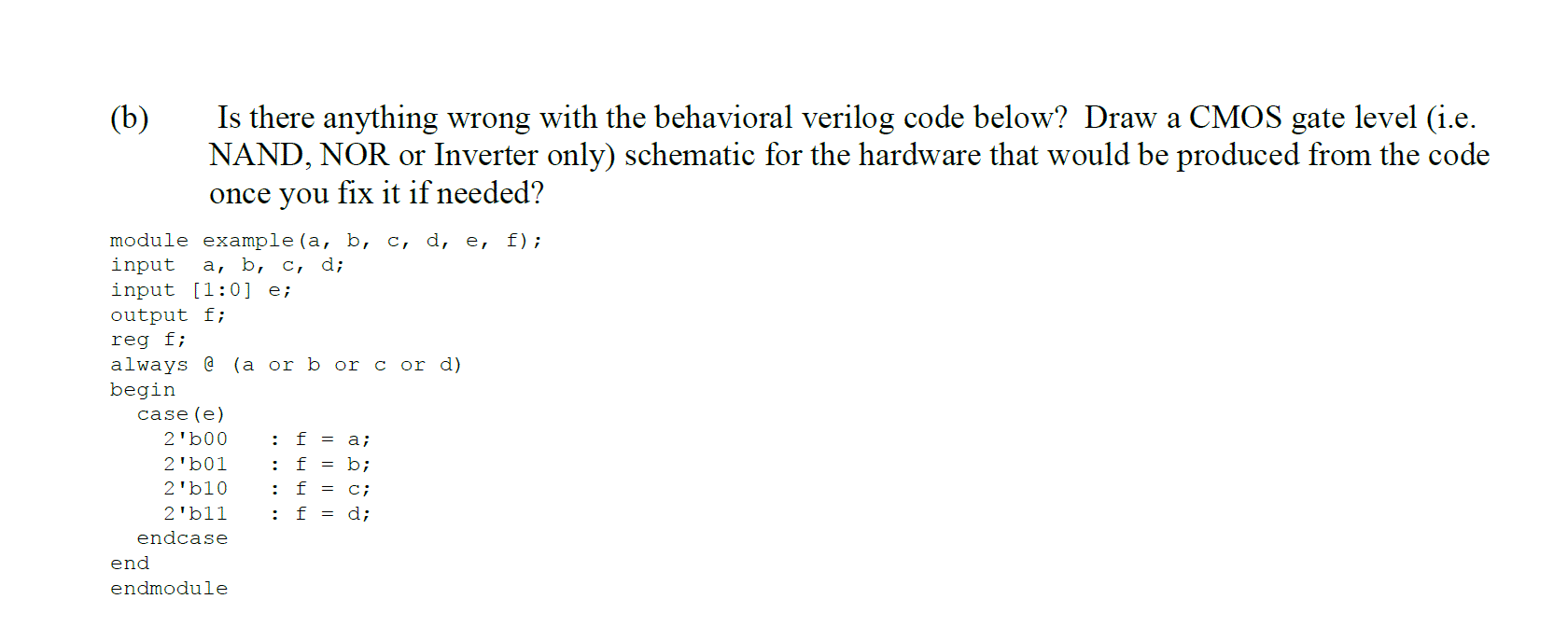

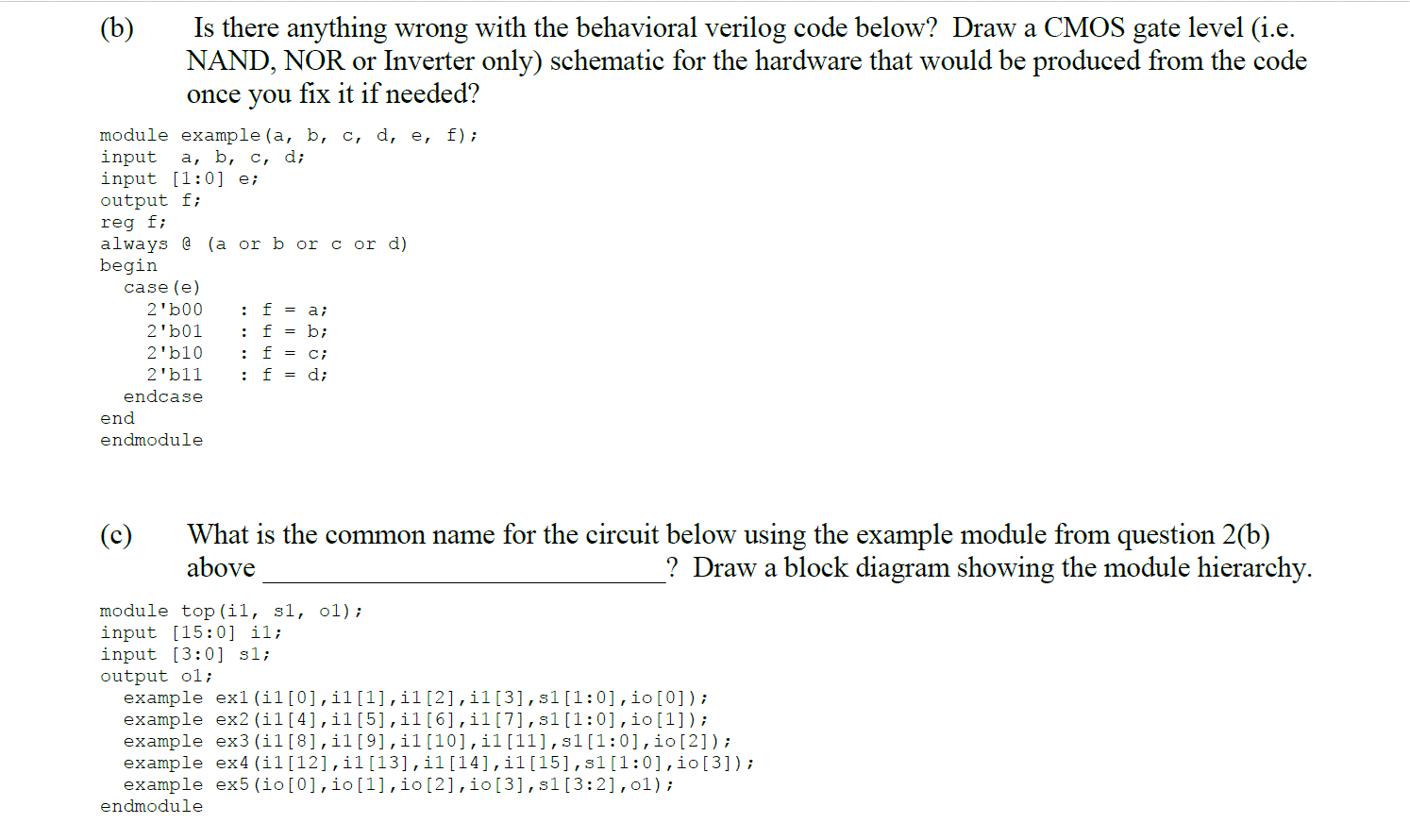

B Is There Anything Wrong With The Behavioral Chegg

| Title: B Is There Anything Wrong With The Behavioral Chegg |

| Format: eBook |

| Number of Pages: 207 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: February 2019 |

| File Size: 2.3mb |

| Read B Is There Anything Wrong With The Behavioral Chegg |

|

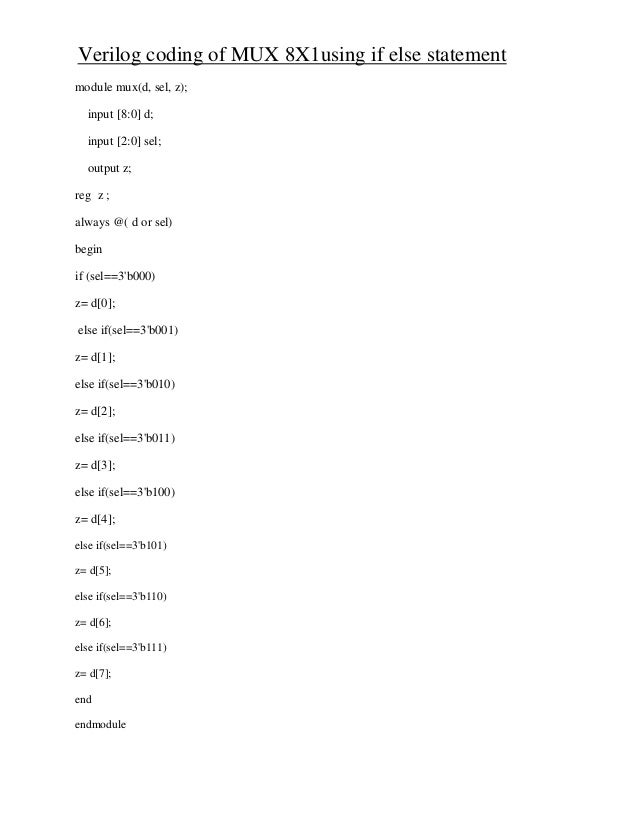

Verilog Coding Of Mux 8 X1

| Title: Verilog Coding Of Mux 8 X1 |

| Format: ePub Book |

| Number of Pages: 180 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: July 2018 |

| File Size: 2.2mb |

| Read Verilog Coding Of Mux 8 X1 |

|

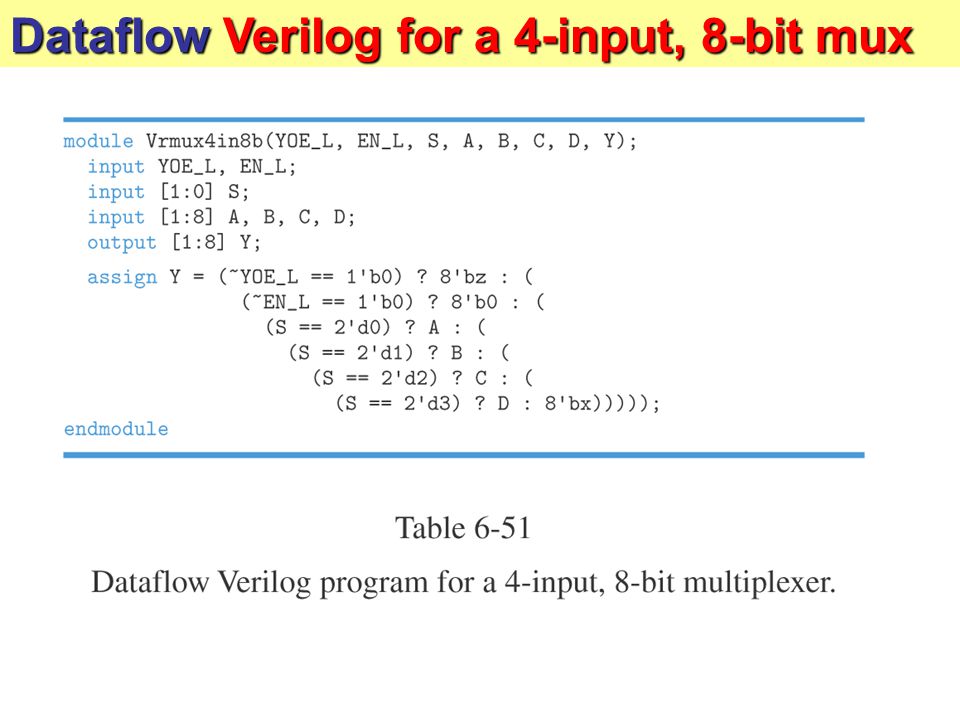

Coding Verilog

| Title: Coding Verilog |

| Format: PDF |

| Number of Pages: 180 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: April 2021 |

| File Size: 2.8mb |

| Read Coding Verilog |

|

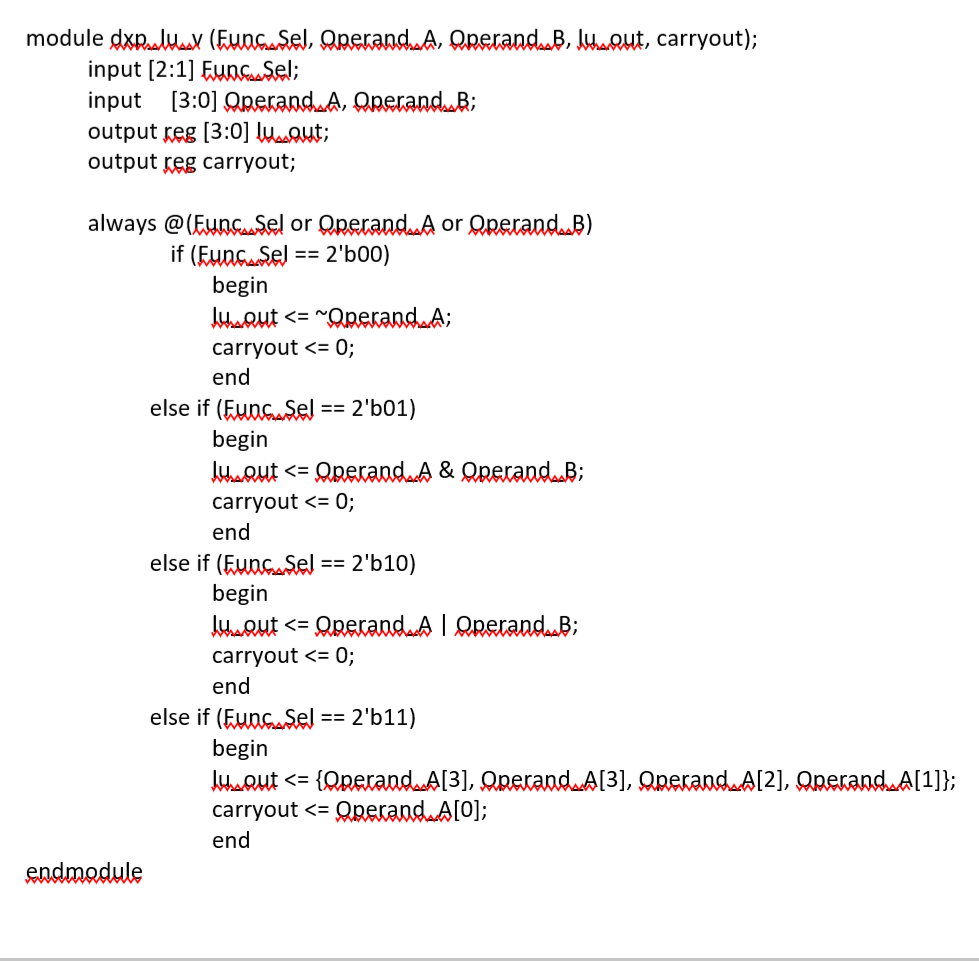

Verilog Code For Alu In Gate Level Vlsi Design Verilog Introduction

| Title: Verilog Code For Alu In Gate Level Vlsi Design Verilog Introduction |

| Format: PDF |

| Number of Pages: 312 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: February 2017 |

| File Size: 2.2mb |

| Read Verilog Code For Alu In Gate Level Vlsi Design Verilog Introduction |

|

B Is There Anything Wrong With The Behavioral Chegg

| Title: B Is There Anything Wrong With The Behavioral Chegg |

| Format: eBook |

| Number of Pages: 131 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: September 2020 |

| File Size: 6mb |

| Read B Is There Anything Wrong With The Behavioral Chegg |

|

Vhdl And Verilog Hdl Lab Manual Notes

| Title: Vhdl And Verilog Hdl Lab Manual Notes |

| Format: eBook |

| Number of Pages: 166 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: October 2019 |

| File Size: 3mb |

| Read Vhdl And Verilog Hdl Lab Manual Notes |

|

Write A Verilog Simulation Code For A 3 To 8 Decoder And A Simulation Code For Homeworklib

| Title: Write A Verilog Simulation Code For A 3 To 8 Decoder And A Simulation Code For Homeworklib |

| Format: PDF |

| Number of Pages: 257 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: November 2019 |

| File Size: 2.6mb |

| Read Write A Verilog Simulation Code For A 3 To 8 Decoder And A Simulation Code For Homeworklib |

|

Write A Verilog Code For Implementation Of 2 Input Chegg

| Title: Write A Verilog Code For Implementation Of 2 Input Chegg |

| Format: ePub Book |

| Number of Pages: 261 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: August 2021 |

| File Size: 2.2mb |

| Read Write A Verilog Code For Implementation Of 2 Input Chegg |

|

Verilog Code For Half And Full Subtractor Using Structural Modeling

| Title: Verilog Code For Half And Full Subtractor Using Structural Modeling |

| Format: eBook |

| Number of Pages: 189 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: April 2017 |

| File Size: 1.4mb |

| Read Verilog Code For Half And Full Subtractor Using Structural Modeling |

|

The Following Pieces Of Behavioral Verilog Code Must Chegg

| Title: The Following Pieces Of Behavioral Verilog Code Must Chegg |

| Format: PDF |

| Number of Pages: 255 pages Verilog Code For And Gate In Behavioural Model |

| Publication Date: February 2020 |

| File Size: 725kb |

| Read The Following Pieces Of Behavioral Verilog Code Must Chegg |

|

Gate level or Structural level. We declare the module as nand_gate. Simulate four input OR gate.

Here is all you need to learn about verilog code for and gate in behavioural model Assign c a. The input and output ports are then declared. An output of one module is an input to another module and this can be performed by using wire. B is there anything wrong with the behavioral chegg write a verilog simulation code for a 3 to 8 decoder and a simulation code for homeworklib demux 1 to 4 gate level verilog code verilog code for alu in gate level vlsi design verilog introduction verilog coding of mux 8 x1 coding verilog The port list includes the output and input ports.

Post a Comment

Post a Comment